# KT915

### IEEE802.11b/g/n Wireless LAN

**Combo Stamp Module**

### DATASHEET

REV: 1.1

DATA: 16.08.2021

This specification may be changed with the improvement of the product. Please refer to the latest version of the usermanual.KERTONG TECHNOLOGY reserves the right of final interpretation and modification of all contents of this specification.

## **Revision History**

| Date       | Revision Content          | Revised By | Version |

|------------|---------------------------|------------|---------|

| 2020/07/25 | - Preliminary             | LIU LEI    | 1.0     |

| 2020/08/16 | - Pin Definition Modified | SHAWN      | 1.1     |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           | *          |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

|            |                           |            |         |

## Contents

| Contents                                | 2  |

|-----------------------------------------|----|

| 1. Introduction                         | 3  |

| 1.1 About KERTONG                       | 3  |

| 1.2 Product Overview                    | 3  |

| 2. Features                             | 4  |

| 2.1 WLAN                                | 4  |

| 3. Specification Table                  | 6  |

| 3.1 General Specification               | 6  |

| 3.2 Voltages (Absolute Maximum Ratings) | 6  |

| 3.3 2.4GHz RF Specification             | 7  |

| 4. Pin Assignments                      | 9  |

| 4.1 Pin Map                             | 9  |

| 4.2 Pin Table                           | 9  |

| 5. Mechanical and Layout Design         | 11 |

| 6. Frequency References                 | 12 |

| 6.1 External Clock Reference            |    |

| 6.2 SDIO v2.0                           | 13 |

| 7.1 Power-up Sequence Timing Diagram    | 14 |

| 7.3 SDIO High Speed Mode Timing Diagram | 16 |

| 8. Recommended Reflow Profile           |    |

| 9. PCB Layout Solder Paste              |    |

| 10. Package Information                 | 20 |

|                                         |    |

| 11. This product is RoHS compliance     |    |

## 1. Introduction

### 1.1 About KERTONG

KERTONG Technologies Inc was established in Shenzhen in 2008. It is located in Baoan, Shenzhen. It is a high-tech enterprise specializing in the radio - related radio frequency series module application and the integrated solution platform of the products. At present, the product lines are: wireless network WIFI access module, wireless routing application module, wireless Bluetooth module, wireless Bluetooth box module, NFC communication module, GPS navigation module, Zigbee control module, wireless communication module and so on, as well as related module application solutions. The company has a complete set of 60 radio frequency integrated testers, 10 communication integrated testers, with a variety of wireless testing standards.

### 1.2 Product Overview

KERTONG Technologies to announce a low-cost and low-power consumption the combo module of KT915 model which has all of the WiFi(IEEE802.11b/g/n), Bluetooth (5.0) functionalities. And the highly integrated module makes the possibilities of web browsing Mini audio; Wireless projector; Bluetooth POS.ect and other applications. With seamless roaming capabilities and advanced security, also could interact with different vendors' 802.11b/g/n Access Points in the wireless LAN.

This KT915 module using the chipset from Rockchip's the RK915B is advanced design techniques and process technology to reduce active and idle power, and designed to address the needs of highly mobile devices that require minimal power consumption and compact size. It includes a power management unit that simplifies the system power topology and allows for operation directly from a rechargeable mobile platform battery while maximizing battery life.

The KT915 module complies with IEEE 802.11 b/g/n standard and it can achieve up to a speed of 72.2Mbps with single stream in 802.11n draft, 54Mbps as specified in IEEE802.11g or 11Mbps for IEEE 802.11b to connect to the wireless LAN. The integrated module provides SDIO interface for WiFi.

## 2. Features

- IEEE802.11b/g/n single-band radio

- SDIO v2.0 host interface for WLAN and UP to 50MHz clock rate

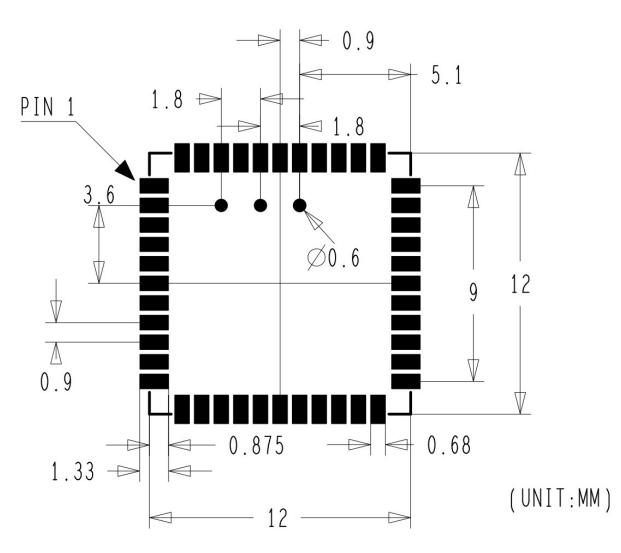

- SZIE 12mm \* 12mm \* 1.5mm (L\*W\*H) LGA package

### 2.1 WLAN

- IEEE 802.11b/g/n single-band radio with an internal power amplifier, LNA, and T/R switch

- Simultaneous WLAN reception with a single antenna

- WLAN host interface options:

- □ SDIO v2.0, including default and high-speed timing.

- □ gSPI—up to a 50 MHz clock rate

- Security:

- □ WEP

- □ WPA™ Personal

- □ WPA2<sup>™</sup> Personal

- □ WMM

- □ WMM-PS (U-APSD)

- □ WMM-SA

- 🗆 WAPI

- □ AES (Hardware Accelerator)

- □ TKIP (host-computed)

- □ WIFI Mode (apsta; ap ; p2p)

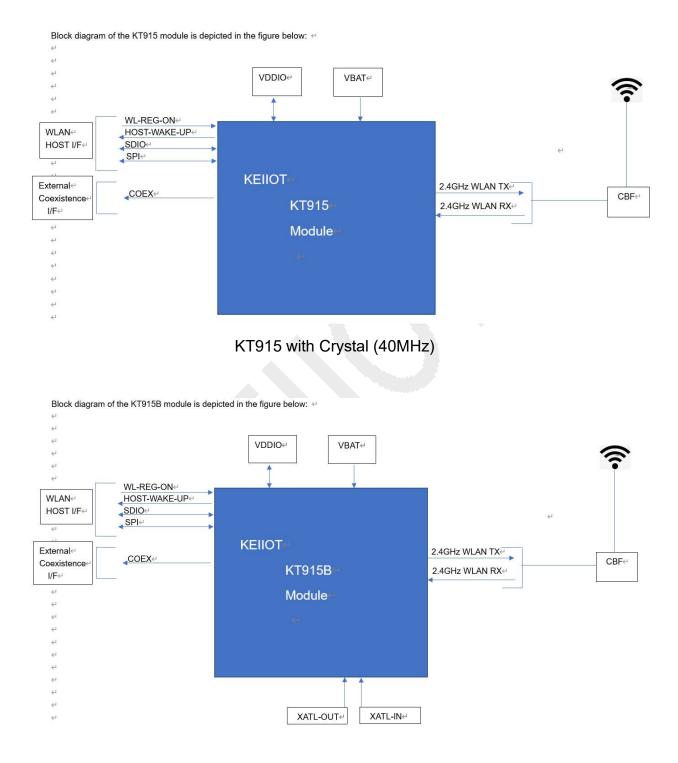

### 2.3 Block Diagram

A simplified block diagram of the KT915 & KT915B module is depicted in the figure below:

KT915B without Crystal (External)

## 3. Specification Table

### 3.1 General Specification

| Major Chipset       | Rockchip RK915B                              |

|---------------------|----------------------------------------------|

| Model Name          | KT915                                        |

| Product Description | Support WiFi functionalities                 |

| Dimension           | L x W x H: 12 x 12 x 1.5mm                   |

| WiFi Host Interface | SDIO v2.0                                    |

| BT Interface        | Null                                         |

| Operating           | -30°C to 85°C                                |

| Storage temperature | -40°C to 85°C                                |

| Humidity            | Operating Humidity 10% to 95% Non-Condensing |

### 3.2 Voltages (Absolute Maximum Ratings)

| Symbol (3.3V)             | Description                | Min.        | Max. | Unit |

|---------------------------|----------------------------|-------------|------|------|

| VBAT Input supply Voltage |                            | 2.97        | 3.63 | V    |

| WL_VIO_SD                 | Digital/ SDIO/ I/O Voltage | 2.97 3.63 V |      |      |

|                           |                            |             |      |      |

| Symbol (1.8V) Description |                            | Min. | Max. | Unit |

|---------------------------|----------------------------|------|------|------|

| VBAT Input supply Voltage |                            | 1.62 | 1.98 | V    |

| WL_VIO_SD                 | Digital/ SDIO/ I/O Voltage | 1.62 | 1.98 | V    |

|                           |                            |      |      |      |

**\*NOTE:** The KT915 module requires two power supplies: VBAT and VDDIO

### 3.3 2.4GHz RF Specification

| Feature                    | Description                                     |  |  |  |  |  |

|----------------------------|-------------------------------------------------|--|--|--|--|--|

| WLAN Standard              | IEEE 802.11b/g/n, WiFi compliant                |  |  |  |  |  |

| Frequency Range            | 2.400 GHz ~ 2.497 GHz (2.4 GHz ISM Band)        |  |  |  |  |  |

| Channels                   | 2.4GHz:Ch1 ~ Ch13                               |  |  |  |  |  |

| Modulation                 | 802.11b : DQPSK, DBPSK, CCK                     |  |  |  |  |  |

|                            | 802.11 g/n : OFDM /64-QAM,16-QAM, QPSK, BPSK    |  |  |  |  |  |

|                            | 802.11b /11Mbps : 16 dBm ± 1.5 dB @ EVM ≤ -9dB  |  |  |  |  |  |

| Output Power               | 802.11g /54Mbps : 13 dBm ± 1.5 dB @ EVM ≤ -26dB |  |  |  |  |  |

|                            | 802.11n /65Mbps : 10 dBm ± 1.5 dB @ EVM ≤ -29dB |  |  |  |  |  |

|                            | - MCS=0 PER @ -85 dBm, typical                  |  |  |  |  |  |

|                            | - MCS=1 PER @ -84 dBm, typical                  |  |  |  |  |  |

| Receive                    | - MCS=2 PER @ -82 dBm, typical                  |  |  |  |  |  |

| Sensitivity                | - MCS=3 PER @ -80 dBm, typical                  |  |  |  |  |  |

| (11n,20MHz)                | - MCS=4 PER @ -77 dBm, typical                  |  |  |  |  |  |

| @10% PER                   | - MCS=5 PER @ -73 dBm, typical                  |  |  |  |  |  |

|                            | - MCS=6 PER @ -71 dBm, typical                  |  |  |  |  |  |

|                            | - MCS=7 PER @ -68 dBm, typical                  |  |  |  |  |  |

|                            | - 6Mbps PER @ -86 dBm, typical                  |  |  |  |  |  |

|                            | - 9Mbps PER @ -85 dBm, typical                  |  |  |  |  |  |

|                            | - 12Mbps PER @ -85 dBm, typical                 |  |  |  |  |  |

| <b>Receive Sensitivity</b> | - 18Mbps PER @ -83 dBm, typical                 |  |  |  |  |  |

| (11g)                      | - 24Mbps PER @ -81 dBm, typical                 |  |  |  |  |  |

| @10% PER                   | - 36Mbps PER @ -78 dBm, typical                 |  |  |  |  |  |

|                            | - 48Mbps PER @ -73 dBm, typical                 |  |  |  |  |  |

|                            | - 54Mbps PER @ -71 dBm, typical                 |  |  |  |  |  |

|                            | - 1Mbps PER @ -88 dBm, typical                  |  |  |  |  |  |

| <b>Receive Sensitivity</b> | - 2Mbps PER @ -88 dBm, typical                  |  |  |  |  |  |

| (11b)                      | - 5.5Mbps PER @ -88 dBm, typical                |  |  |  |  |  |

| @8% PER                    | - 11Mbps PER @ -87 dBm, typical                 |  |  |  |  |  |

| Data Pato                  | 802.11b : 1, 2, 5.5, 11Mbps                     |  |  |  |  |  |

| Data Rate                  | 802.11g : 6, 9, 12, 18, 24, 36, 48, 54Mbps      |  |  |  |  |  |

| Data Rate           | 802.11n: 6.5, 13, 19.5, 26, 39, 52, 58.5, 65Mbps         |

|---------------------|----------------------------------------------------------|

| (20MHz ,Long        |                                                          |

| Data Rate           | 802.11n : 7.2, 14.4, 21.7, 28.9, 43.3, 57.8, 65,72.2Mbps |

| (20MHz ,short       |                                                          |

| Movimum Input Loval | 802.11b : -10 dBm                                        |

| Maximum Input Level | 802.11g/n : -20 dBm                                      |

| Antenna Re          | Small antennas with 0~2 dBi peak gain                    |

Copyright © 2008-2021 | www.kertong.com.cn | All rights reserved

## 4. Pin Assignments

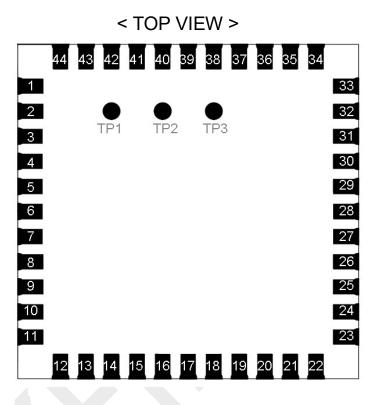

### 4.1 Pin Map

KeiiOt

#### 4.2 Pin Table

| NO | Name     | Туре | Description                          |  |  |  |

|----|----------|------|--------------------------------------|--|--|--|

| 1  | GND      | —    | Ground connections                   |  |  |  |

| 2  | WL_ANT   | I/O  | WLAN (RF->TX/RX) patch               |  |  |  |

| 3  | GND      | —    | Ground                               |  |  |  |

| 4  | NC       | —    | Floating (Don't connected to ground) |  |  |  |

| 5  | NC       | —    | Floating (Don't connected to ground) |  |  |  |

| 6  | NC       | —    | Floating (Don't connected to ground) |  |  |  |

| 7  | NC       | —    | Floating (Don't connected to ground) |  |  |  |

| 8  | NC       | —    | Floating (Don't connected to ground) |  |  |  |

| 9  | VBAT     | Р    | Main power voltage source input      |  |  |  |

| 10 | XTAL_IN  | I    | Crystal input                        |  |  |  |

| 11 | XTAL_OUT | 0    | Crystal output                       |  |  |  |

|    | - KT915 datasheet_V1.1_16082021 .doc   Shawn Xiao |     |                                            |  |

|----|---------------------------------------------------|-----|--------------------------------------------|--|

| 12 | WL_REG_ON                                         | I   | Internal regulators power enable/disable   |  |

| 13 | WL_HOST_WAKE                                      | 0   | WLAN to wake-up HOST                       |  |

| 14 | SDIO_DATA_2                                       | I/O | SDIO data line 2                           |  |

| 15 | SDIO_DATA_3                                       | I/O | SDIO data line 3                           |  |

| 16 | SDIO_DATA_CMD                                     | I/O | SDIO command line                          |  |

| 17 | SDIO_DATA_CLK                                     | I/O | SDIO clock line                            |  |

| 18 | SDIO_DATA_0                                       | I/O | SDIO data line 0                           |  |

| 19 | SDIO_DATA_1                                       | I/O | SDIO data line 1                           |  |

| 20 | GND                                               | —   | Ground connections                         |  |

| 21 | VIN_LDO_OUT                                       | Р   | Internal Buck voltage generation pin       |  |

| 22 | VDDIO                                             | Р   | I/O Voltage supply input                   |  |

| 23 | VIN_LDO                                           | Р   | Internal Buck voltage generation pin       |  |

| 24 | LPO                                               | I   | External Low Power Clock input (32.768KHz) |  |

| 25 | NC                                                | _   | Floating (Don't connected to ground)       |  |

| 26 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 27 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 28 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 29 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 30 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 31 | GND                                               |     | Ground connections                         |  |

| 32 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 33 | GND                                               | _   | Ground connections                         |  |

| 34 | NC                                                | —   | Low asserting reset for Bluetooth core     |  |

| 35 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 36 | GND                                               | —   | Ground connections                         |  |

| 37 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 38 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 39 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 40 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 41 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 42 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 43 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 44 | NC                                                | —   | Floating (Don't connected to ground)       |  |

| 45 | NC                                                | 0   | NC                                         |  |

| 46 | NC                                                | 0   | NC                                         |  |

| 47 | NC                                                | 0   | NC                                         |  |

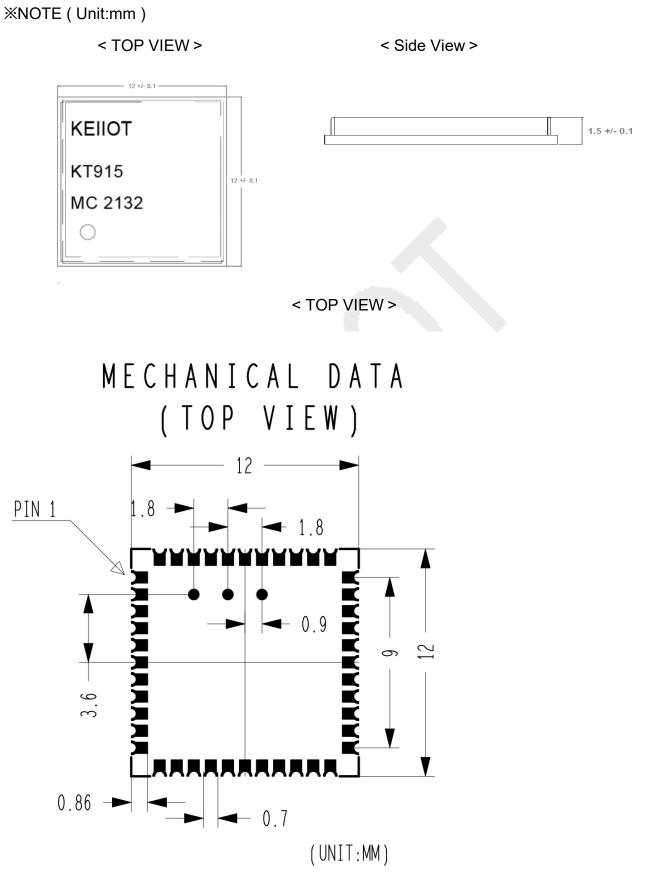

## 5. Mechanical and Layout Design

## 6. Frequency References

### 6.1 External Clock Reference

The module uses a secondary low-frequency sleep clock for low-power mode timing. Either the internal low-precision LPO or an external 32.768 kHz precision oscillator is required. The internal LPO frequency range is approximately 33 kHz  $\pm$  30% over process, voltage, and temperature, which is adequate for some applications. However, one trade-off caused by this wide LPO tolerance is a small current consumption increase during power save mode that is incurred by the need to wake up earlier to avoid missing beacons.

| Parameter                                    | Specification            | Units   |

|----------------------------------------------|--------------------------|---------|

| Nominal input frequency                      | 32.768                   | kHz     |

| Frequency accuracy                           | $\pm 30$                 | ppm     |

| Duty cycle                                   | 30 - 70                  | %       |

| Input signal amplitude                       | 400 to 1800              | mV, p-p |

| Signal type                                  | Square-wave or sine wave | -       |

| Inputimpodopoo                               | >100k                    | Ω       |

| Input impedance                              | <5                       | pF      |

| Clock jitter (integrated over 300Hz – 15KHz) | <10,000                  | ppm     |

External LPO signal characteristics:

External LPO signal characteristics:

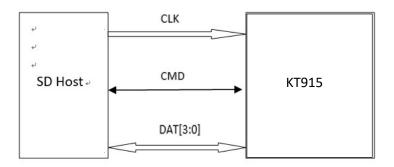

### 6.2 SDIO v2.0

The module supports SDIO version 2.0 for both 1-bit (25Mbps) and 4-bit (100Mbps), as well as high speed 4-bit (50 MHz clocks – 200 Mbps). Then has the ability to map the interrupt signal on a GPIO pin. This out-of-band interrupt signal notifies the host when the WLAN device wants to turn on the SDIO interface. The ability to force control of the gated clocks from within the WLAN chip is also provided.

Three functions are supported:

■ Function 0 standard SDIO function. The maximum block size is 32 bytes.

■ Function 1 backplane function to access the internal System-on-a-Chip (SoC) address space. The maximum block size is 64 bytes.

■ Function 2 WLAN function for efficient WLAN packet transfer through DMA. The maximum block size is 512 bytes.

**SDIO PIN Descriptions**

| SD 4-Bit Mode |                          |  |  |  |

|---------------|--------------------------|--|--|--|

| DATA0         | Data line 0              |  |  |  |

| DATA1         | Data line 1 or Interrupt |  |  |  |

| DATA2         | Data line 2              |  |  |  |

| DATA3         | Data line 3              |  |  |  |

| CLK           | Clock                    |  |  |  |

| CMD           | Command line             |  |  |  |

|               |                          |  |  |  |

Signal Connections to SDIO Host

## 7. Interface Timing Diagram

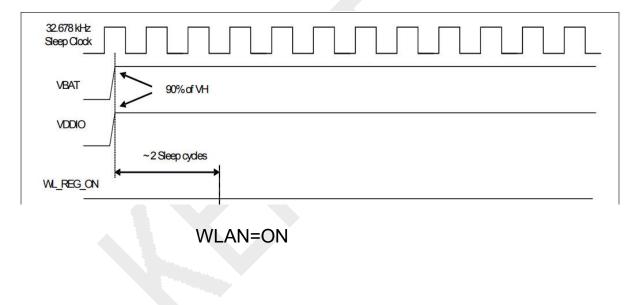

### 7.1 Power-up Sequence Timing Diagram

The module has signals that allow the host to control power consumption by enabling, WLAN and internal regulator blocks. These signals are described below.Additionally, diagrams are provided to indicate proper sequencing of the signals for carious operating states. The timing value indicated are minimum required values: longer delays are also acceptable.

WL\_REG\_ON: Used by the PMU to power up the WLAN section. When this pin is high, the regulators are enabled and the WLAN section is out of reset. When this pin is low the WLAN section is in reset.

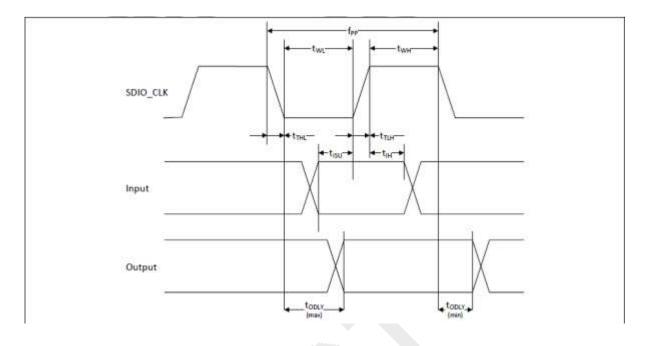

#### SDIO Default Mode Timing Diagram

| Parameter                                  | Symbol      | Minimum      | Typical          | Maximum | Unit |

|--------------------------------------------|-------------|--------------|------------------|---------|------|

| SDIO CLK (All values are refferred to mini | imum VIH an | d maximum VI | L <sup>b</sup> ) |         |      |

| Frequency-Data Transfer mode               | fPP         | 0            | -                | 25      | MHz  |

| Frequency-Identification mode              | fOD         | 0            | -                | 400     | kHz  |

| Clock low time                             | tWL         | 10           | 7                | -       | ns   |

| Clock high time                            | tWH         | 10           |                  |         | ns   |

| Clock rise time                            | tTLH        |              | <b>1</b>         | 10      | ns   |

| Clock low time                             | tTHL        | -            | -                | 10      | ns   |

| Inputs: CMD, DAT (referenced to CLK)       |             |              |                  |         |      |

| Input setup time                           | tISU        | 5            | -                | -       | ns   |

| Input hold time                            | tIH         | 5            | -                | -       | ns   |

| Outputs: CMD, DAT (referenced to CLK)      |             |              |                  |         |      |

| Output delay time – Data Transfer mode     | tODLY       | 0            | 2                | 14      | ns   |

| Output delay time - Identification mode    | tODLY       | 0            | -                | 50      | ns   |

a. Timing is based on CL ≤ 40pF load on CMD and Data.

b. min(Vih) = 0.7 x VDDIO and max(Vil) = 0.2 x VDDIO.

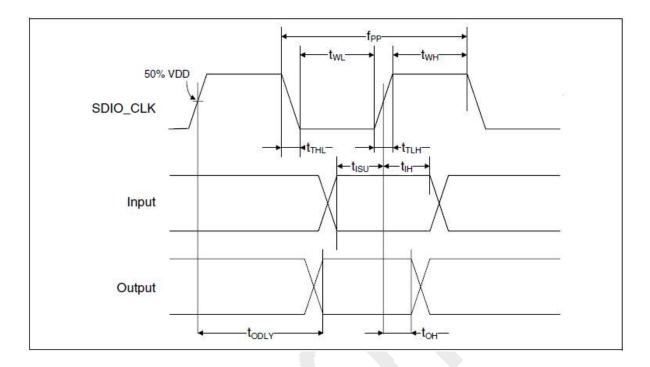

### 7.3 SDIO High Speed Mode Timing Diagram

| Parameter                                                                        | Symbol  | Minimum | Typical | Maximum          | Unit |  |

|----------------------------------------------------------------------------------|---------|---------|---------|------------------|------|--|

| SDIO CLK (All values are refferred to minimum VIH and maximum VIL <sup>b</sup> ) |         |         |         |                  |      |  |

| Frequency-Data Transfer mode                                                     | fPP     | 0       | 5       | 50               | MHz  |  |

| Frequency-Identification mode                                                    | fOD     | 0       | -       | 400              | kHz  |  |

| Clock low time                                                                   | tWL     | 7       | -       | -                | ns   |  |

| Clock high time                                                                  | tWH     | 7       | -       | -                | ns   |  |

| Clock rise time                                                                  | tTLH    | 2       | 2       | 3                | ns   |  |

| Clock low time                                                                   | tTHL    | -       | 2       | 3                | ns   |  |

| Inputs: CMD, DAT (referenced to CLK)                                             |         |         |         |                  |      |  |

| Input setup time                                                                 | tISU    | 6       | -       | -                | ns   |  |

| Input hold time                                                                  | tlH     | 2       | -       | ( <del>-</del> ) | ns   |  |

| Outputs: CMD, DAT (referenced to CLK)                                            |         |         |         |                  |      |  |

| Output delay time – Data Transfer mode                                           | tODLY   | -       | -       | 14               | ns   |  |

| Output hold time                                                                 | tOH     | 2.5     | -       | -                | ns   |  |

| Total system capacitance (each line)                                             | CL      | -       | -       | 40               | pF   |  |

|                                                                                  | D - t - |         |         |                  |      |  |

a. Timing is based on CL ≤ 40pF load on CMD and Data.

b. min(Vih) = 0.7 x VDDIO and max(Vil) = 0.2 x VDDIO.

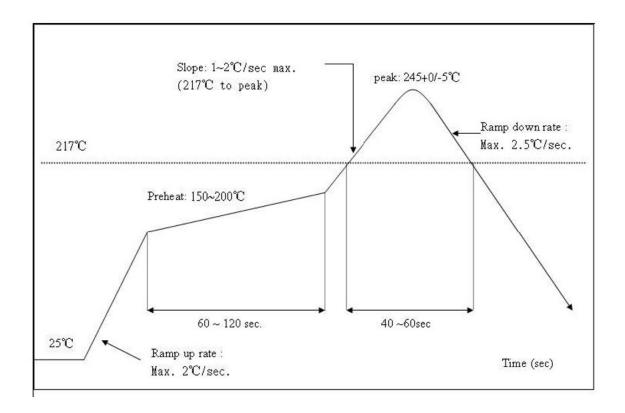

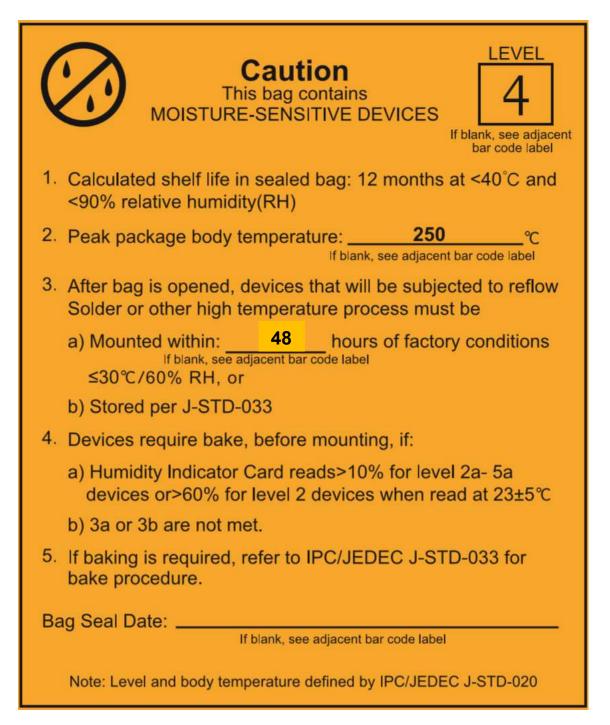

## 8. Recommended Reflow Profile

Referred to IPC/JEDEC standard.

Peak Temperature :<250°C Number

of Times : ≤2 times

#### ENVIRONMENTAL.

Operating : \*Operating Temperature: -10°C to +70 °C \*Relative Humidity: 5-90% (non-condensing)

| Storage            |                                |

|--------------------|--------------------------------|

| *Temperature:      | -40°C to +80°C (non-operating) |

| Relevant Humidity: | 5-95% (non-condensing)         |

MTBF caculation \*Over 150,000hour

NOTE: it must use N2 for reflow and suggest the concentration of oxygenless than 5000 ppm

## 9. PCB Layout Solder Paste

EXAMPLE BOARD LAYOUT

- O Module Specifications : W:0.65mm \* L:0.95mm pitch 0.9 mm

- The proposed design W:0.65~0.75 mm \* L:1.33mm. Consider not place other parts in the peripheral area of 1 mm ~ 1.5 mm to facilitate additional amount of solder for PCB pad.

- We Suggest the thickness of Stencil between 0.12 mm ~0.15mm, the W between 0.6~0.65mm and the L between L1.5~1.6mm.

- If the thickness of the stencil is thinner, we suggest to adding more solder, to increase the wetting ability. Depends on different production situation, if the stencil thickness is 0.08~0.1mm, and the module nearby area is no more space for expending soldering area, we will suggest to increase the stencil thickness to increase the wetting ability.

- O The major consideration parts of stencil design is to increase the solder paste wetting

<sup>Xiao</sup> ability.

- O Module Specifications L 0.7mm

- O The design for PCB Pad : L:0.8mm

- We recommend the apertures for stencil L:0.5mm~0.6mm

- In order to avoid highness impact caused solder paste thickness, the stencil open size can be appropriately retracted

Xiao

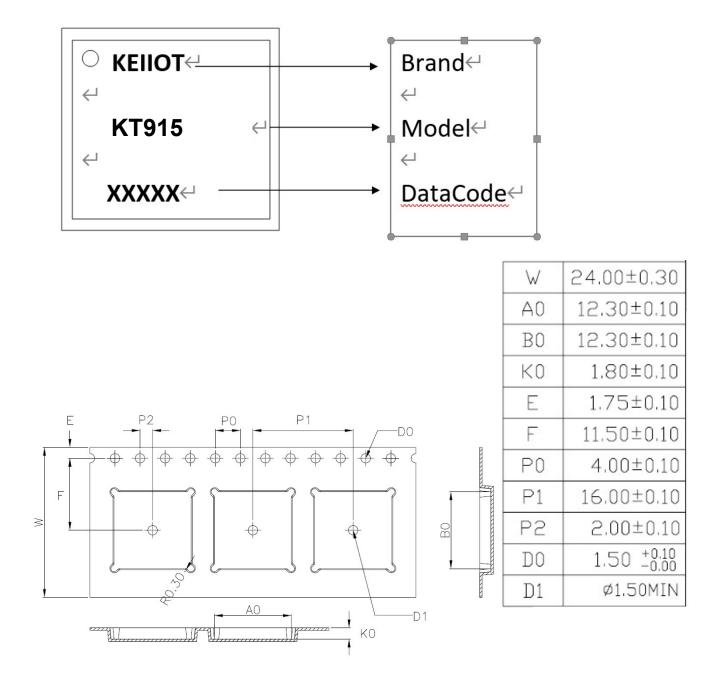

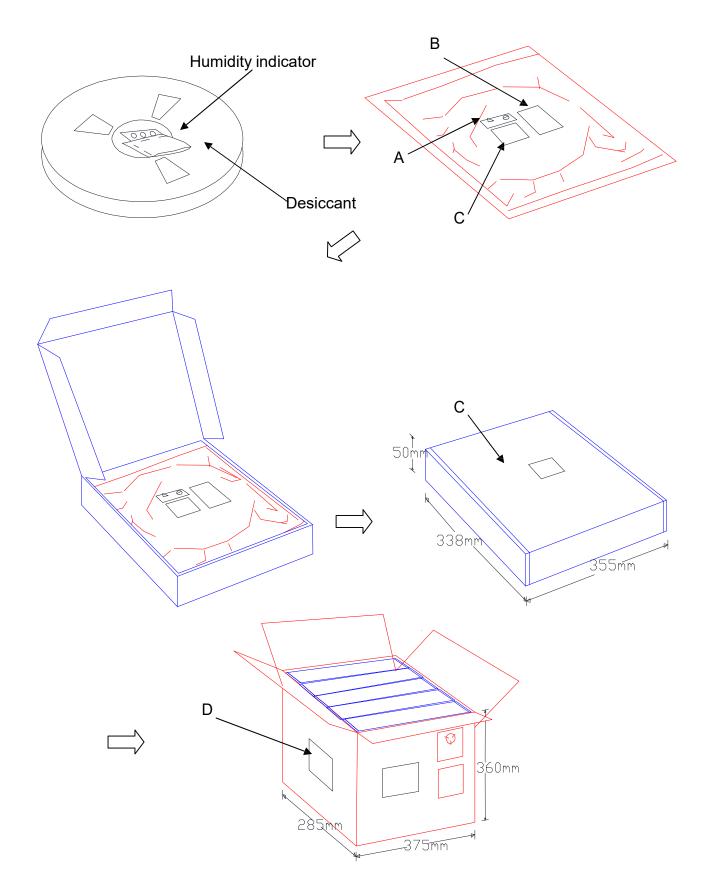

## 10. Package Information

- 1. 10 sprocket hole pitch cumulative tolerance  $\pm 0.20$ .

- 2. Carrier camber is within 1 mm in 250 mm.

- 3. Material : Black Conductive Polystyrene Alloy.

- 4. All dimensions meet EIA-481-D requirements.

- 5. Thickness : 0.30±0.05mm.

- 6. Packing length per 22" reel : 98.5 Meters.(1:3)

- 7. Component load per 13" reel : 1500 pcs.

- KT915 datasheet\_V1.1\_16082021 .doc | Shawn

- Xiao 1> 1500pcs of per disc

- 2> 1500pcs \* 5 =7500pcs ( one Cartoon )

### 11. This product is RoHS compliance

#### Wireless module before the SMT Note:

When customers Open stencil must be sure the hole bigger to the Wireless module plate, please press 1 to 1 and 0.7 mm is widened to open outward, the thickness of 0.12 mm.

① Can't get the wifi module bare hands when needs,must we wear the gloves and static ring.

The furnace temperature according to the size of the customer the mainboard ,generally like to stick on a tablet standard temperature of 250 + - 5,can do 260 + - 5. Storage and use Wifi module control should pay attention to the following matters:

- ① Module of the storage life of vacuum packaging:

- 1-1. Storage life: 12 months. Storage conditions:<40 . Relative °C humidity:<90%R.H.

- 1-2. 1-2.After this bag is opened , devices that will be subjected to infrared reflow, vaporphase reflow, or equivalent processing must be

- Check the humidity card :stored at ≤20%RH.If :30%~40%(pink)or greater than 40%(red).Labeling module has moisture absorption.

- ① Mounthed within 168 hours at factory conditions of:  $\leq Ct 30\%$ ,  $\leq 60\%$ R.H.

- ② Once opened, the workshop the preservation of life for 168 hours.

- 1-4. If baking is required, devices may be baked for:

- ① Modules must be to remove module moisture problem.

- ② Baking temperature: 125, 8 hours. ℃

- ③ After baking, put proper amount of desiccant to seal packages.

- 1-5. The actual number of module vacuum packing which is based on the actual number of packages to the customer requirements.

- 2. Module reel packaging items as follows.

- 2-1. Storage life: 12 months. Storage conditions:<40. Relative °C humidity:<90%R.H.

- 2-2. Module apart packing after 168 hours, To launch patch need to bake, to remove the module hygroscopic, baking temperature conditions: 125°C, 8hours.

- 2-3. The actual number of module reel packing which is based on the actual number of packages to the customer requirements.

- 3. Module pallet packaging items as follows:

- 3-1. Storage life: 3 months. Storage conditions:<40 . Relative °C humidity:<90%R.H.

- 3-2. Module if not used within 48 hours, before launch the need for baking, baking temperature: 125 , 8 hours. ℃

- 3-3. Pallet packaging each plate is 100 PCS. The actual number of module pallet packing which is based on the actual number of packages to the customer requirements.

### 12. MSL Level / Storage Condition

**XNOTE** : Accumulated baking time should not exceed 96hrs